## **GJCET**

# System-in-Package (SiP) Solutions

Semiconductor companies are continually faced with complex integration challenges as consumers want their electronics to be smaller, faster and higher performance with more and more functionality packed into a single device. This demand for miniaturization and modularization of

functionality in a single package combined with the increasing cost per transistor of advanced Silicon nodes beyond 28nm is rapidly moving the microelectronics industry toward system level integration.

Advanced packaging has a significant impact on addressing these challenges. Semiconductor companies are increasingly looking to their outsourcing partners to provide highly integrated advanced packaging solutions for their end products. System-in-Package (SiP) is a high performance solution that can meet the current and future demands for greater system performance, increased functionality, reduced power consumption and reduced form factor in a wide range of markets and applications.

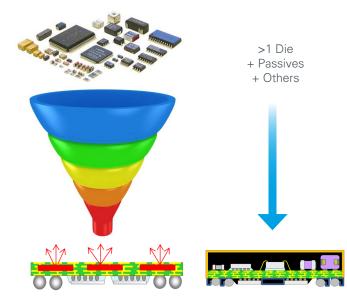

SiP is a functional electronic system or sub-system that includes two or more heterogeneous semiconductor die (often from different technology nodes optimized for their individual functionalities), usually with passive components.

## **Advantages of SiP**

To meet the need for increased integration, improved electrical performance, reduced power consumption, faster speed and smaller device sizes, several advantages are driving the industry towards SiP solutions including:

- » Thinner / smaller form factor than individually packaged components

- Increased performance and functional integration

- » Design flexibilities

- Better electromagnetic interference (EMI) isolation

- » Reduced system board space and complexity

- » More room for the battery

- » Simplified SMT assembly process

- » Cost effective "plug-and-play" solutions

- » Faster time-to-market (TTM)

- » One stop turnkey solution Wafer to fully tested SiP modules

With these advantages, SiP is able to address some of the limitations of silicon (Si) level integration (commonly known as System-on-Chip or SoC), including design complexities, long development cycles, manufacturability, intellectual property (IP) and legal issues, longer time-to-market and higher costs. SiP provides a high performance packaging solution that is scalable, cost effective and can be easily implemented in an electronic device.

## **Comprehensive Capabilities for SiP Markets and Applications**

We have a comprehensive SiP portfolio to serve multiple markets and end applications. Today, SiP and miniaturized modules are being utilized in a number of markets such as mobile devices, Internet of Things (IoT), wearables, healthcare, industrial, automotive, computing and communication networks. Each SiP solution varies in complexity based on the number and functionality of the components required by each application.

Below are some examples of our SiP solutions and endmarket applications.

| SiP Package<br>Configurations                    | Examples | Features                                                                                                                                       | Target Applications                                                                                      |

|--------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Stacked Die<br>Module                            |          | <ul><li>LGA/BGA</li><li>Thin/stacked die</li><li>Passives</li></ul>                                                                            | <ul> <li>SSD (removable &amp; embedded)</li> <li>Baseband / application processor (Wearables)</li> </ul> |

| Substrate<br>Module                              |          | <ul> <li>LGA/BGA</li> <li>Bare die or over mold</li> <li>IPD, passives</li> </ul>                                                              | <ul> <li>Filters</li> <li>Power amplifier (PA) modules</li> <li>Connectivity combo modules</li> </ul>    |

| fcFBGA/LGA<br>SiP<br>Hybrid (flip chip +         |          | <ul> <li>Passives, WLCSP,<br/>packaged components</li> <li>Coreless or cored<br/>substrates</li> </ul>                                         | <ul> <li>Controller modules</li> <li>Power amplifier/ Power<br/>amplifier duplexer modules</li> </ul>    |

| wirebond)<br>SiP - single sided                  |          | substrates                                                                                                                                     | RF Front-end modules (FEM)                                                                               |

| Hybrid SiP -<br>double sided                     |          | <ul> <li>Double sided assembly with active and passives</li> <li>Coreless or cored substrates</li> </ul>                                       | <ul> <li>RF Front-end modules (FEM)</li> <li>Connectivity combo<br/>modules</li> </ul>                   |

| eWLB SiP                                         |          | <ul> <li>Multi die</li> <li>Embedded passives</li> </ul>                                                                                       | <ul><li>Connectivity</li><li>PMIC, CODEC</li><li>Power amplifier modules</li></ul>                       |

|                                                  |          |                                                                                                                                                | <ul> <li>Application processor +<br/>memory</li> <li>RF MEMS</li> </ul>                                  |

| fcBGA SiP                                        |          | <ul> <li>Multi die</li> <li>Packaged and bare die</li> <li>DRAM and passives</li> <li>Advanced thermal managment</li> <li>Lage body</li> </ul> | <ul><li>CPU/GPU + memory</li><li>Networking, gaming</li></ul>                                            |

|                                                  |          |                                                                                                                                                | Automotive                                                                                               |

| Antenna-in-<br>Package - SiP<br>Laminate<br>eWLB |          | <ul> <li>Embedded or discrete antenna</li> <li>PoP antenna</li> <li>Fan-out or laminate base</li> <li>Low loss materials</li> </ul>            | <ul> <li>5G communication</li> <li>Automotive radar, LIDAR</li> </ul>                                    |

| eWLB-PoP &<br>2.5D SiP                           |          | <ul> <li>eWLB-PoP</li> <li>Fine pitch and high I/O</li> </ul>                                                                                  | <ul> <li>High-end application<br/>processors</li> <li>CPU/GPU</li> <li>High bandwidth</li> </ul>         |

## **Design, Assembly and Test Capabilities**

### **Design and Simulation**

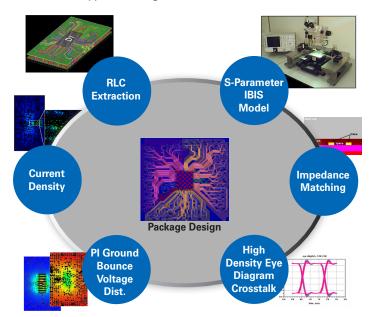

In the drive for miniaturization, semiconductor companies face complex issues in developing highly integrated package designs. Our experienced R&D and engineering teams are here to support customers faced with complex SiP integration requirements. Our capabilities and services in SiP module design are supported by advanced electrical, mechanical and thermal simulation.

Typical Design and Simulation Flow

Our Surface Mount Technology (SMT) design rules are being advanced through refinements in materials and process technologies to enable tighter component-to-component placement, and molding technologies and compounds are being improved to enable lower mold cap profiles and smaller dimensions. Our design rules are the most advanced, enabling extreme miniaturization. We work with advanced substrate materials with fine line width/spacing (L/S), reduced dielectric thickness, and coreless design to address the reduced form factor requirements of next generation applications while enabling a lower cost.

Vertical integration brings about higher component density and optimizes the board space needed in the end device, allowing for a larger battery space or smaller overall size. Our expertise in embedded wafer level ball grid array (eWLB) using advanced L/S and via density design rules, with the cost effective integration of passives and multiple embedded die in advanced eWLB SiP configurations offers further form factor reduction and lower package profiles.

## Assembly

SiP solutions require multiple packaging technologies such as fine pitch flip chip, wire bonding, wafer level packaging (WLP) and eWLB, Integrated Passive Devices (IPDs) and embedded die to meet the specific requirements for a product. The specific technology used in each application varies in complexity based on the number and type of components as defined by the application and cost requirements. In addition to the packaging technology, there are important technical requirements for an SiP solution, including advanced substrates, high density SMT placement, enhanced molding processes, and electromagnetic interference (EMI) shielding.

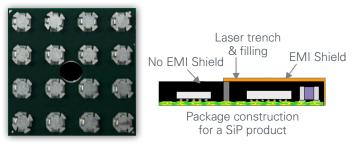

EMI shielding has become essential for applications such as RF/mobile connectivity and mmWave (5G) SiPs. As operating frequencies increase and devices become more complex, electronic devices are more susceptible to electromagnetic interference. EMI shields can prevent interference from either a device generating interference out to the world or the device picking interference from outside sources into itself.

SiP provides the ability to partition different segments of the system functionality while EMI shielding protects different circuit segments from EMI interferences and noise susceptibility. We offer a portfolio of shielding options, including fully automated in-line conformal shielding, compartmental and selective shielding to serve the diverse needs of current and next generation RF/mobile connectivity and mmWave (5G) SiPs.

Connectivity SiP with Selective EMI Shield

Our manufacturing capabilities such as advanced SMT with high accuracy component placement, advanced doublesided molding for complex SiP applications, EMI conformal shielding and high process yields, coupled with our high volume SMT line and fully automated loading/unloading process in the EMI shielding process, ensure that our customers receive fast, high quality, cost effective solutions.

As one of the first companies in the industry to integrate and fabricate passive devices at the Si level, we are able to produce IPDs which are significantly smaller,

thinner and higher performing than standard discrete passive devices and embed them in very close proximity to the active die, providing significant performance, size reduction and device integration in SiP configurations.

## **Test Services**

To meet the need for increased integration, improved electrical performance, reduced power consumption, faster speed and smaller device sizes, several advantages are driving the industry towards SiP solutions including:

- » Experience in RF ATE mass production on Advantest RF (< 6 GHz), Teradyne RF system (< 6GHz ), LTX-CX (< 6 GHz) and NI-PXI (<6 GHz) platform, utilizing multiple sites (up to 16 sites)</li>

- » Capability on Microwave option (GEN4/UltraWave12G) for Catalyst/IFLEX/uFLEX (Teradyne RF)

- Experience in RF mass production volume test and multiple sites (up to 16 sites and 600M units over the past 5 years)

- » Proven RF Test Development Engineering on 60GHz Transceiver, GPS, RFFE Envelope Tracker, etc.

- » EMI and Electromagnetic Susceptibility (EMS) measurement and characterization capabilities, including near field testing

EMI and EMS Measurement

## **Full Turnkey Solutions**

We look forward to working with you to serve your complex system integration needs. Our industry leading advanced capabilities, from design to assembly and test, and multiple assembly platforms (laminate, eWLB and wirebond), along with our flexible business model, high throughput and high yield automated processes enable us to deliver diverse solutions for our customer base.

As demand for complex, highly integrated electronics devices continues to grow and evolve in the semiconductor industry, you can rely on our advanced technology and manufacturing experience to deliver the optimum SiP solution for your competitive integration needs.

SiP Assembly

#### JCET Group Co., Ltd. www.jcetglobal.com

The JCET logo is a registered trademark of JCET Group Co., Ltd. Trademark registered in the People's Republic of China (registration number: 3000529). All other product names and other company names herein are for identification purposes only and may be the trademarks or registered trademarks of their respective owners. This brochure as well as datasheets herein are for presentation purposes only. JCET or its subsidiaries do not warrant or make any representation whatsoever, express, implied or statutory, as to the accuracy, adequacy, reliability, completeness or otherwise. Readers are advised to seek professional advice at all time and obtain independent verification of the information contained herein before making any decision. JCET reserves the right to change the information at any time and without notice.